VHDL Signal vs Variable: Understanding Key Differences and Practical Uses

What is VHDL and Why It Matters

VHDL (VHSIC Hardware Description Language) is one of the most widely used languages for describing digital systems and integrated circuits. Based on Ada and Pascal, it allows engineers to model complex digital systems before physical implementation. I've been using VHDL for over a decade, and I'm always amazed at how it bridges the gap between conceptual design and physical hardware.

Unlike traditional programming languages that execute instructions sequentially, VHDL describes hardware that operates concurrently. This fundamental difference introduces unique concepts like signals and variables that behave quite differently from similar constructs in software programming languages. Have you ever wondered why your VHDL code doesn't behave as expected? The answer might lie in how you're using signals and variables.

In my experience working with FPGA designs, I've seen countless newcomers struggle with the concepts of signals and variables. The confusion often stems from trying to apply software programming paradigms to hardware description. Remember, we're not writing software that executes sequentially—we're describing hardware that operates concurrently. This distinction is crucial to understand before diving deeper into signals and variables.

Understanding Signals in VHDL

Signals in VHDL represent physical connections between components in a digital circuit, much like wires connecting different parts of the hardware. They are the primary means of communication between concurrent processes and components. What makes signals special is that they maintain a history of values and enable the modeling of time-dependent behavior essential to digital circuits.

One key aspect of signals is their scheduled updates. When you assign a value to a signal, the assignment doesn't take effect immediately. Instead, it's scheduled to occur after a delta delay or after a specified time delay. This behavior accurately models the propagation delays present in real hardware. I remember spending hours debugging a design only to realize I had misunderstood how signal assignments were being scheduled!

Signals can be declared in various scopes, including entity declarations, architecture bodies, blocks, and packages. The scope of a signal determines its visibility and accessibility within your VHDL code. Here's an example of signal declaration:

In this example, I've declared three signals inside the architecture: TempData, FlagComplete, and BitCounter. Each serves a specific purpose in our digital design. The FlagComplete and BitCounter signals include initial values, which will be assigned to them at the start of simulation or synthesis.

Understanding Variables in VHDL

Unlike signals, variables in VHDL store information that is local to processes and subprograms. They represent temporary storage locations used for computation within sequential code blocks. The most distinctive characteristic of variables is that they update immediately when assigned a new value. There's no concept of scheduling or delta delays with variables.

Variables can only be declared and used within processes, functions, and procedures—the sequential parts of VHDL code. They cannot be used for communication between concurrent processes. I've found variables particularly useful for implementing complex algorithms within a process or for keeping track of temporary values during calculations.

Here's an example showing variable declaration and usage:

In this example, I've declared three variables (TempResult, AccumulatedValue, and Counter) inside a process. These variables are used for intermediate calculations and are only visible within the process. Notice how they're assigned values using the ":=" operator, while signals use the "<=" operator for assignment.

Key Differences Between Signals and Variables

| Aspect | Signals | Variables |

|---|---|---|

| Basic Nature | Represent physical connections (wires) | Represent temporary storage locations |

| Update Timing | Scheduled updates (delta or time delays) | Immediate updates |

| Value History | Maintains history of values | Only stores current value |

| Scope & Visibility | Can be declared in entity, architecture, package, or block | Only declared within processes and subprograms |

| Assignment Operator | Uses "<=" operator | Uses ":=" operator |

| Concurrent Access | Can be accessed by multiple concurrent processes | Only accessible within its declaring process |

| Hardware Representation | Directly maps to physical wires and registers | Often optimized away during synthesis |

| Syntax | signal name: type [:= initial_value]; | variable name: type [:= initial_value]; |

Understanding these differences is crucial for writing correct and efficient VHDL code. Misusing signals and variables is a common source of errors in VHDL designs. I once spent an entire weekend tracking down a bug that was caused by using a signal where a variable should have been used, resulting in unexpected timing behavior.

When to Use Signals vs Variables

Choosing between signals and variables isn't always straightforward. Based on my experience, here are some guidelines to help you make the right choice:

Use Signals When:

- You need to communicate between concurrent processes or entities

- You want to model hardware connections or wires

- You need to represent registered values that change on clock edges

- You need to model timing behavior or propagation delays

- You want to observe the value in a waveform during simulation

Use Variables When:

- You need temporary storage within a sequential process

- You're implementing complex algorithms with multiple intermediate steps

- You need immediate updates to values within a process

- You want to optimize for performance in sequential code

- You're creating loop counters or accumulators within a process

In my designs, I typically use signals for any value that needs to persist between clock cycles or that communicates between different parts of the design. Variables are reserved for temporary calculations within processes. This approach has served me well in keeping my code clean and avoiding common pitfalls.

Sometimes, you might be tempted to use a variable when a signal would be more appropriate, especially when trying to optimize your code. However, remember that modern synthesis tools are quite good at optimizing VHDL code, so it's usually better to write clear, correct code rather than trying to outsmart the tools.

Common Pitfalls and Misconceptions

Even experienced VHDL developers sometimes fall into traps when working with signals and variables. Here are some common pitfalls to avoid:

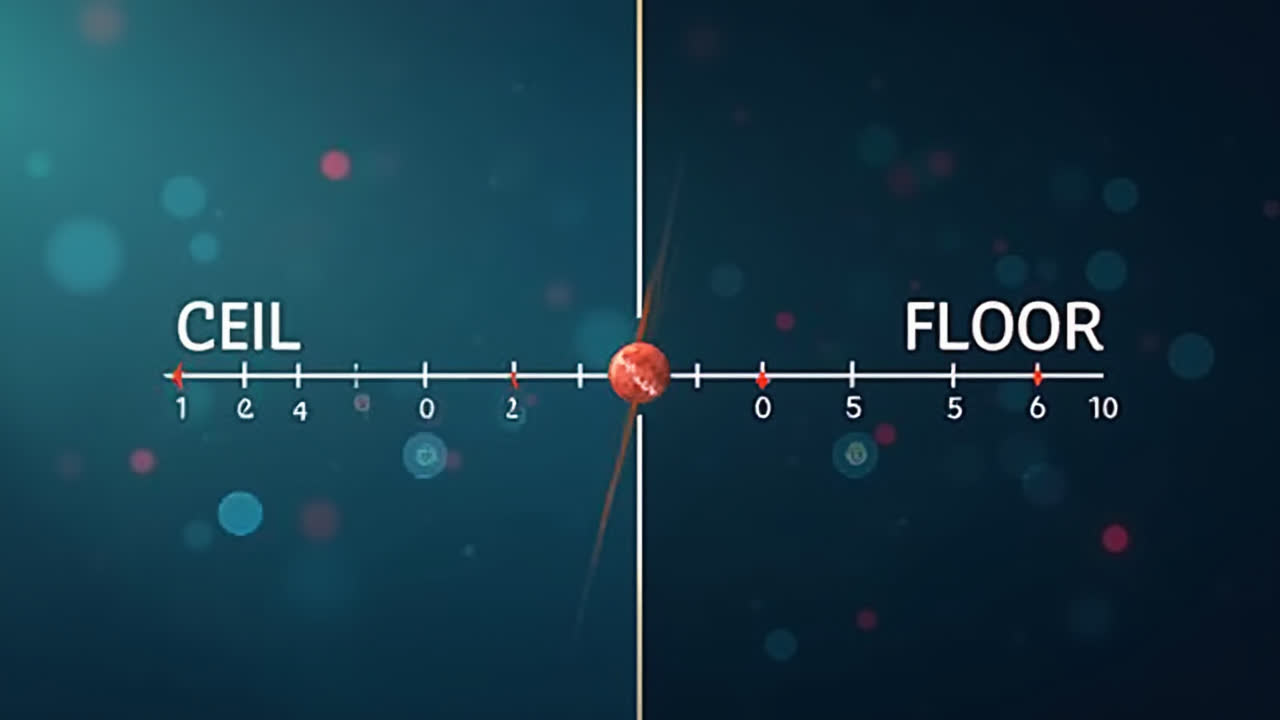

Signal Assignment Scheduling

A frequent misconception is thinking that signal assignments take effect immediately within a process. They don't! All signal assignments are scheduled to occur after the current process suspends. This can lead to unexpected behavior if you're counting on a signal's value changing immediately after assignment.

In this example, the evaluation of "Count = 10" uses the value of Count before the increment, not after. To fix this, you would either need to use a variable for Count or restructure your code.

Variable Persistence

Another common mistake is assuming that variables retain their values between process activations. In reality, variables are reinitialized to their default values each time the process is entered, unless you declare them as "shared" variables (which come with their own issues). If you need a value to persist between process activations, use a signal instead.

Mixing Signal and Variable Assignments

Mixing signal and variable assignments in complex ways can lead to code that's difficult to understand and debug. It's generally a good practice to use variables for intermediate calculations and then assign the final results to signals at the end of your process.

I once inherited a codebase where the previous developer had liberally mixed signal and variable assignments in complex ways. It took me weeks to understand the actual behavior of the code, and eventually, I had to refactor it completely to make it maintainable.

Practical Examples and Use Cases

Let's look at some practical examples that demonstrate the proper use of signals and variables in real-world designs.

Example 1: Counter with Enable

In this example, Count is appropriately implemented as a signal because it represents a register that needs to retain its value between clock cycles.

Example 2: Complex Calculation

Here, Temp1 and Temp2 are appropriately implemented as variables because they're just temporary values used within the calculation process. The final result is assigned to a signal that can be used elsewhere in the design.

These examples demonstrate clean, maintainable code that uses signals and variables appropriately. By following these patterns, you can avoid many common errors and create more reliable VHDL designs.

Frequently Asked Questions About VHDL Signals and Variables

Can I use a variable to communicate between two processes?

No, you cannot use a regular variable to communicate between two processes in VHDL. Variables are local to the process or subprogram in which they're declared. If you need to communicate between processes, you must use a signal. In newer versions of VHDL (VHDL-2008 and later), there is a concept of "shared variables" with protected types that can be used for inter-process communication, but these come with additional complexity and are generally not recommended for beginners. Signals are almost always the correct choice for communication between concurrent processes.

Why does my VHDL simulation behave differently from the synthesized hardware?

Differences between simulation and synthesis often stem from timing issues or from using VHDL constructs that are not synthesizable. Signal assignments in simulation follow the defined delta delay model, which may not perfectly match the actual timing in hardware. Additionally, variable assignments happen immediately in simulation, but the synthesis tool may implement them differently in hardware. To minimize these differences, follow synthesizable coding practices: use synchronous logic where possible, avoid complex combinational feedback loops, and be careful with signal assignments within combinational processes. Always thoroughly test your design in post-synthesis simulation to catch any differences before hardware implementation.

What happens if I don't initialize a signal or variable in VHDL?

If you don't explicitly initialize a signal or variable in VHDL, it will take on the default value for its type. For standard types: integers default to 0, booleans to FALSE, std_logic to 'U' (undefined), and enumerated types to their first value. In simulation, uninitialized signals and variables behave according to these default values. However, in actual hardware, uninitialized signals typically power up in an unknown state, which can lead to unpredictable behavior. Best practice is to always include a reset mechanism in your design to explicitly initialize all important signals to known states, regardless of their default values in simulation.

Conclusion: Making the Right Choice

Understanding the differences between signals and variables is fundamental to writing effective VHDL code. Signals represent physical connections with scheduled updates and value history, making them suitable for inter-process communication and modeling hardware connections. Variables, with their immediate updates and local scope, are perfect for temporary storage and complex sequential calculations.

The choice between signals and variables impacts not only how your code behaves in simulation but also how efficiently it maps to actual hardware. By making informed decisions about when to use each, you can create VHDL designs that are both correct and efficient.

In my years of experience with VHDL design, I've found that a good rule of thumb is: when in doubt, use a signal. While variables have their place in optimizing sequential code, signals more naturally represent the concurrent nature of hardware and are less prone to subtle timing errors.

Remember, VHDL is not just another programming language—it's a hardware description language. By embracing its unique concepts rather than fighting against them, you'll become a more effective digital designer. So, next time you're deciding between a signal and a variable, take a moment to consider the hardware you're trying to describe. Your future self (and your colleagues) will thank you!